#### **FEATURES**

- Fast Cycle Times: 20/25/30 ns

- Selectable 36/18/9-Bit Word Width for Both Input Port and Output Port

- Byte-Order-Reversal Function (i.e., 'Big-Endian' ↔ 'Little-Endian' Conversion)

- 16-mA-I<sub>OL</sub> Three-State Outputs

- Automatic Byte Parity Checking

- Selectable Byte Parity Generation

- Five Status Flags: Full, Almost-Full, Half-Full, Almost-Empty, and Empty

- All FIFO Status Flags are Synchronous (AE, HF, AF Through Programming of Control Register)

- Programmed Values may be entered from either Port

- Two Enable Control Signals for each Port

- Mailbox Register with Synchronized Flags

- Asynchronous Data-Bypass Function

- 'Smart' Data-Retransmit Function

- Configurable for Paralleled FIFO Operation (72-Bit Data Width)

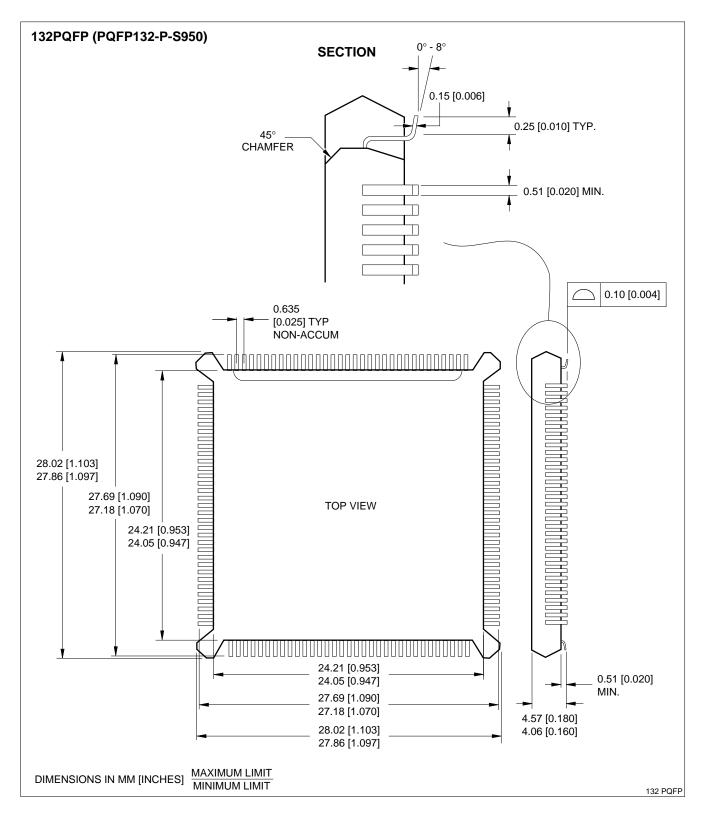

- Space-Saving PQFP and TQFP <sup>1</sup> Packages

- PQFP-to-PGA Package Conversion<sup>2</sup>

#### This is a final data sheet; except that all references to the TQFP package have Preliminary status.

#### FUNCTIONAL DESCRIPTION

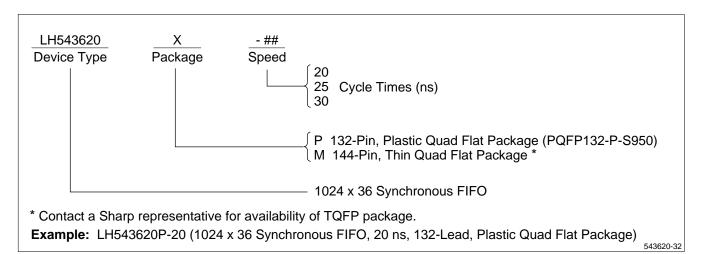

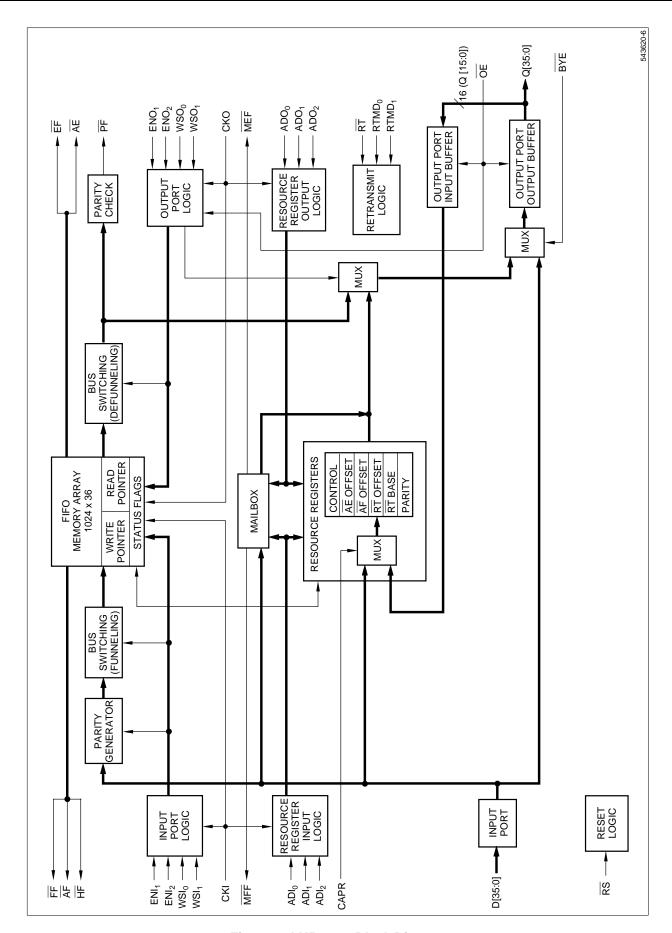

The LH543620 is a FIFO (First-In, First-Out) memory device, based on fully-static CMOS RAM technology, capable of containing up to 1024 36-bit words. It can replace four or more nine-bit-wide FIFOs in many applications.

The input port and the output port operate independently of each other. Write operations are performed on the rising edge of the input clock CKI, and enabled by two enabled signals ENI<sub>1</sub>, ENI<sub>2</sub>. Read operations are performed on the rising edge of the output clock CKO and enabled by two enabled signals ENO<sub>1</sub>, ENO<sub>2</sub>.

Five status flags are available to monitor the memory array status: Full, Almost-Full, Half-Full, Almost-Empty, and Empty. The Almost-Full and Almost-Empty flags are initialized to a default offset of eight locations from their respective boundaries, but they are each programmable over the entire FIFO depth.

Both the input port and the output port may be set independently to operate at three data-word widths: 36 bits, 18 bits, or 9 bits. This setting may be changed during system operation. The LH543620 can perform Byte-Order-Reversal on the four nine-bit bytes of each 36-bit data word passing through it, thus accomplishing 'Big Endian'  $\leftrightarrow$  'Little Endian' conversion.

When data is read out of the FIFO a byte-parity check is performed. The parity flag is used to indicate that a parity error was detected in one of the 9-bit bytes of the output word.

Parity generation, when selected, creates the parity bit of each 8-bit byte of the input word. The result is written into the MSB-bit of each 9-bit byte, overwriting the previous contents of the bit. The default is odd parity. However, the FIFO may be programmed to use even parity.

The LH543620 has a data-bypass mode that connects the output port to the input port asynchronously. A mailbox facility with Synchronized Flags is provided from the input port to the output port.

The LH543620's 'Smart-Retransmit' capability sets the internal-memory read pointer to any arbitrary memory location. The 'Smart-Retransmit' capability includes a Marking Function and a Programmable Offset to support data communication and digital signal processing applications.

For PQFP-to-PGA conversion for thru-hole board designs, Sharp recommends ITT Pomona Electronics' SMT/PGA Generic Converter model #5853<sup>®</sup>. This converter maps the LH543620 132-pin PQFP to a generic 13 × 13, 132-pin PGA (100-mil pitch). For more information, contact Sharp or ITT Pomona Electronics at 1500 East Ninth Street, Pomona, CA 91766, (909) 469-2900.

Figure 1. LH543620 Block Diagram

**DESCRIPTION**

# PIN DESCRIPTIONS (SUMMARY)

| PIN NAME                           | PIN<br>TYPE * | DESCRIPTION                        |  |  |  |

|------------------------------------|---------------|------------------------------------|--|--|--|

| DATABUS                            |               |                                    |  |  |  |

| D[35:0]                            | I             | 36-Bit Input-Port Databus          |  |  |  |

| Q[15:0]                            | I/O/Z         | Three-State 36-Bit Output-         |  |  |  |

| Q[35:16]                           | O/Z           | Port Databus                       |  |  |  |

|                                    | С             | LOCKS                              |  |  |  |

| CKI                                | I             | Input-Port Clock                   |  |  |  |

| СКО                                | I             | Output-Port Clock                  |  |  |  |

| AS                                 | YNCHRO        | NOUS CONTROL                       |  |  |  |

| RS                                 | I             | Master Reset                       |  |  |  |

| ŌĒ                                 | I             | Output Enable                      |  |  |  |

| BYE                                | I             | Data-Bypass Enable                 |  |  |  |

| CAPR                               | ı             | Command-Address Port<br>Reference  |  |  |  |

| CONTR                              | OL SIGN       | ALS SYNCHRONOUS                    |  |  |  |

|                                    | TO THE        | INPUT CLOCK                        |  |  |  |

| ENI <sub>1</sub> ,ENI <sub>2</sub> | I             | Input-Port Enables                 |  |  |  |

| ADI[2:0]                           | I             | Input-Port Address                 |  |  |  |

| WSI[1:0]                           | I             | Input-Port Word-Width<br>Selection |  |  |  |

| STAT                               | US FLAC       | SS SYNCHRONOUS                     |  |  |  |

|                                    | TO THE        | INPUT CLOCK                        |  |  |  |

| FF                                 | 0             | Full Flag                          |  |  |  |

| ĀF                                 | 0             | Almost-Full Flag                   |  |  |  |

| HF <sup>1</sup>                    | 0             | Half-Full Flag                     |  |  |  |

| MFF                                | 0             | Mailbox-Full Flag                  |  |  |  |

| CONTR                                                    | CONTROL SIGNALS SYNCHRONOUS |                                       |  |  |

|----------------------------------------------------------|-----------------------------|---------------------------------------|--|--|

| TO THE OUTPUT CLOCK                                      |                             |                                       |  |  |

| ENO <sub>1</sub> ,ENO <sub>2</sub> I Output-Port Enables |                             |                                       |  |  |

| ADO[2:0] I Output-Port Address                           |                             |                                       |  |  |

| WSO[1:0] I Output-Port Word-Width Selection              |                             |                                       |  |  |

| RTMD[1:0]   Retransmit Mode Control                      |                             |                                       |  |  |

| RT   Retransmit                                          |                             |                                       |  |  |

| STATUS FLAGS SYNCHRONOUS                                 |                             |                                       |  |  |

| Т                                                        | O THE C                     | OUTPUT CLOCK                          |  |  |

| AE O Almost-Empty Flag                                   |                             |                                       |  |  |

| EF O Empty Flag                                          |                             |                                       |  |  |

| PF O Parity-Error Flag                                   |                             |                                       |  |  |

| PF                                                       | 0                           | Parity-Error Flag                     |  |  |

| MEF                                                      | 0                           | Parity-Error Flag  Mailbox-Empty Flag |  |  |

| MEF                                                      | 0                           |                                       |  |  |

| MEF                                                      | 0                           | Mailbox-Empty Flag                    |  |  |

PIN

TYPE \*

**PIN NAME**

<sup>\*</sup> I = Input, O = Output, V = Voltage, Z = High-Impedance

The half-full flag is user-selectable to be synchronized to either CKI or CKO.

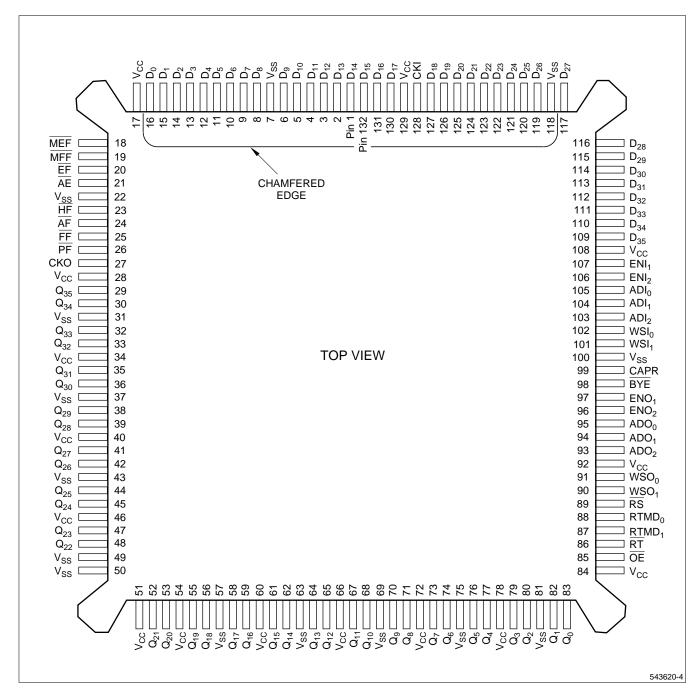

#### **PIN CONNECTIONS**

Figure 2. Pin Connections for 132-Pin PQFP Package (Top View)

# **PIN LIST**

| I III LIOI      | DIV. 1.10 |

|-----------------|-----------|

| PIN NAME        | PIN NO.   |

| D <sub>14</sub> | 1         |

| D <sub>13</sub> | 2         |

| D <sub>12</sub> | 3         |

| D <sub>11</sub> | 4         |

| D <sub>10</sub> | 5         |

| D <sub>9</sub>  | 6         |

| D <sub>8</sub>  | 8         |

| D <sub>7</sub>  | 9         |

| D <sub>6</sub>  | 10        |

| D <sub>5</sub>  | 11        |

| D <sub>4</sub>  | 12        |

| D <sub>3</sub>  | 13        |

| D <sub>2</sub>  | 14        |

| D <sub>1</sub>  | 15        |

| D <sub>0</sub>  | 16        |

| MEF             | 18        |

| MFF             | 19        |

| EF              | 20        |

| ĀĒ              | 21        |

| HF              | 23        |

| ĀF              | 24        |

| FF              | 25        |

| PF              | 26        |

| СКО             | 27        |

| Q <sub>35</sub> | 29        |

| Q <sub>34</sub> | 30        |

| Q <sub>33</sub> | 32        |

| Q <sub>32</sub> | 33        |

| Q <sub>31</sub> | 35        |

| Q <sub>30</sub> | 36        |

| Q <sub>30</sub> | 38        |

| Q <sub>29</sub> | 39        |

| Q <sub>28</sub> | 41        |

| Q <sub>27</sub> | 41        |

| Q <sub>26</sub> |           |

|                 | 44        |

| Q <sub>24</sub> | 45        |

| Q <sub>23</sub> | 47        |

| Q <sub>22</sub> | 48        |

| Q <sub>21</sub> | 52        |

| Q <sub>20</sub> | 53        |

| Q <sub>19</sub> | 55        |

| Q <sub>18</sub> | 56        |

| Q <sub>17</sub> | 58        |

| Q <sub>16</sub> | 59        |

| PIN NAME          | PIN NO. |

|-------------------|---------|

| Q <sub>15</sub>   | 61      |

| Q <sub>14</sub>   | 62      |

| Q <sub>13</sub>   | 64      |

| Q <sub>12</sub>   | 65      |

| Q <sub>11</sub>   | 67      |

| Q <sub>10</sub>   | 68      |

| Q <sub>9</sub>    | 70      |

| Q <sub>8</sub>    | 71      |

| Q <sub>7</sub>    | 73      |

| Q <sub>6</sub>    | 74      |

| Q <sub>5</sub>    | 76      |

| Q <sub>4</sub>    | 77      |

| Q <sub>3</sub>    | 79      |

| Q <sub>2</sub>    | 80      |

| Q <sub>1</sub>    | 82      |

| Q <sub>0</sub>    | 83      |

| <del>OE</del>     | 85      |

| RT                | 86      |

| RTMD <sub>1</sub> | 87      |

| RTMD <sub>0</sub> | 88      |

| RS                | 89      |

| WSO <sub>1</sub>  | 90      |

| WSO <sub>0</sub>  | 91      |

| ADO <sub>2</sub>  | 93      |

| ADO <sub>1</sub>  | 94      |

| ADO <sub>0</sub>  | 95      |

| ENO <sub>2</sub>  | 96      |

| EN0 <sub>1</sub>  | 97      |

| BYE               | 98      |

| CAPR              | 99      |

| WSI <sub>1</sub>  | 101     |

| WSI <sub>0</sub>  | 102     |

| ADI <sub>2</sub>  | 103     |

| ADI₁              | 104     |

| ADI <sub>0</sub>  | 105     |

| ENI <sub>2</sub>  | 106     |

| ENI <sub>1</sub>  | 107     |

| D <sub>35</sub>   | 109     |

| D <sub>34</sub>   | 110     |

| D <sub>33</sub>   | 111     |

| D <sub>32</sub>   | 112     |

| D <sub>31</sub>   | 113     |

| D <sub>30</sub>   | 114     |

| D <sub>29</sub>   | 115     |

| PIN NAME        | PIN NO. |

|-----------------|---------|

| D <sub>28</sub> | 116     |

| D <sub>27</sub> | 117     |

| D <sub>26</sub> | 119     |

| D <sub>25</sub> | 120     |

| D <sub>24</sub> | 121     |

| D <sub>23</sub> | 122     |

| D <sub>22</sub> | 123     |

| D <sub>21</sub> | 124     |

| D <sub>20</sub> | 125     |

| D <sub>19</sub> | 126     |

| D <sub>18</sub> | 127     |

| CKI             | 128     |

| D <sub>17</sub> | 130     |

| D <sub>16</sub> | 131     |

| D <sub>15</sub> | 132     |

| Vss             | 7       |

| V <sub>CC</sub> | 17      |

| V <sub>SS</sub> | 22      |

| Vcc             | 28      |

| V <sub>SS</sub> | 31      |

| V <sub>CC</sub> | 34      |

| Vss             | 37      |

| V <sub>CC</sub> | 40      |

| V <sub>SS</sub> | 43      |

| V <sub>CC</sub> | 46      |

| V <sub>SS</sub> | 49      |

| Vss             | 50      |

| V <sub>CC</sub> | 51      |

| V <sub>CC</sub> | 54      |

| Vss             | 57      |

| V <sub>CC</sub> | 60      |

| V <sub>SS</sub> | 63      |

| V <sub>CC</sub> | 66      |

| V <sub>SS</sub> | 69      |

| Vcc             | 72      |

| V <sub>SS</sub> | 75      |

| V <sub>CC</sub> | 78      |

| Vss             | 81      |

| V <sub>CC</sub> | 84      |

| V <sub>CC</sub> | 92      |

| Vss             | 100     |

| V <sub>CC</sub> | 108     |

| Vss             | 118     |

| V <sub>CC</sub> | 129     |

|                 |         |

# ABSOLUTE MAXIMUM RATINGS 1

| PARAMETER                                                    | RATING                                     |

|--------------------------------------------------------------|--------------------------------------------|

| Supply Voltage to Vss Potential                              | –0.5 V to 7 V                              |

| Signal Pin Voltage to V <sub>SS</sub> Potential <sup>2</sup> | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| DC Output Current <sup>3</sup>                               | ± 75 mA                                    |

| Storage Temperature Range                                    | -65°C to 150°C                             |

| Power Dissipation (Package Limit)                            | 2.5 Watts (Quad Flat Pack)                 |

#### NOTES:

- 1. Stresses greater than those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions outside those indicated in the 'Operating Range' of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Negative undershoot of 1.5 V in amplitude is permitted for up to 10 ns, once per cycle.

- 3. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

#### **OPERATING RANGE**

| SYMBOL         | PARAMETER                 | MIN  | MAX       | UNIT |

|----------------|---------------------------|------|-----------|------|

| T <sub>A</sub> | Temperature, Ambient      | 0    | 70        | οС   |

| Vcc            | Supply Voltage            | 4.5  | 5.5       | V    |

| Vss            | Supply Voltage            | 0    | 0         | V    |

| VIL            | Logic LOW Input Voltage 1 | -0.5 | 0.8       | V    |

| VIH            | Logic HIGH Input Voltage  | 2.2  | Vcc + 0.5 | V    |

#### NOTE:

1. Negative undershoot of 1.5 V in amplitude is permitted for up to 10 ns, once per cycle.

## **DC ELECTRICAL CHARACTERISTICS** (Over Operating Range)

| SYMBOL           | PARAMETER                                     | TEST CONDITIONS                                                                                        | MIN | TYP  | MAX | UNIT |

|------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| ILI              | Input Leakage Current                         | V <sub>CC</sub> = 5.5 V, V <sub>IN</sub> = 0 V To V <sub>CC</sub>                                      | -10 |      | 10  | μΑ   |

| I <sub>LO</sub>  | I/O Leakage Current                           | $\overline{OE} \ge V_{IH}, \ 0 \ V \le V_{OUT} \le V_{CC}$                                             | -10 |      | 10  | μΑ   |

| V <sub>OL</sub>  | Logic LOW Output Voltage                      | I <sub>OL</sub> = 16.0 mA                                                                              |     |      | 0.4 | V    |

| V <sub>OH</sub>  | Logic HIGH Output Voltage                     | $I_{OH} = -8.0 \text{ mA}$                                                                             | 2.4 |      |     | V    |

| I <sub>CC</sub>  | Average Supply Current 1,2                    | Measured at f <sub>C</sub> = maximum                                                                   |     | 205  | 380 | mA   |

| I <sub>CC2</sub> | Average Standby Supply Current <sup>1,3</sup> | All Inputs = V <sub>IHMIN</sub> (Clock idle)                                                           |     | 40   | 85  | mA   |

| lcc3             | Power-Down Supply Current <sup>1</sup>        | All Inputs = V <sub>CC</sub> ,<br>Outputs - open,<br>Control - deasserted,<br>Clocks = V <sub>CC</sub> |     | 0.01 | 1.0 | mA   |

#### NOTE:

- I<sub>CC</sub>, I<sub>CC2</sub>, and I<sub>CC3</sub> are dependent upon actual output loading, and I<sub>CC</sub> is also dependent on cycle times.

Specified values are with outputs open (for I<sub>CC</sub>: C<sub>L</sub> = 0 pF); and, for I<sub>CC</sub>, operating at minimum cycle times.

- 2.  $I_{CC}$  (MAX): Using worst case conditions and data pattern.  $I_{CC}$  (TYP): Using  $V_{CC} = 5$  V and average data pattern.

- 3.  $I_{CC2}$  (TYP): Using  $V_{CC}$  = 5 V and  $T_A$  = 25°C.

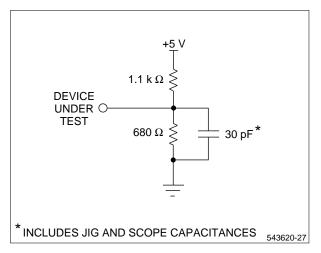

## **AC TEST CONDITIONS**

| PARAMETER                              | RATING     |  |  |

|----------------------------------------|------------|--|--|

| Input Pulse Levels                     | Vss to 3 V |  |  |

| Input Rise and Fall Times (10% to 90%) | 3 ns       |  |  |

| Output Reference Levels                | 1.5 V      |  |  |

| Input Timing Reference Levels          | 1.5 V      |  |  |

| Output Load, Timing Tests              | Figure 3   |  |  |

# **CAPACITANCE** 1,2

| PARAMETER                                  | RATING |

|--------------------------------------------|--------|

| C <sub>IN</sub> MAX. (Input Capacitance)   | 8 pF   |

| C <sub>OUT</sub> MAX. (Output Capacitance) | 10 pF  |

#### NOTES:

- 1. Sample tested only.

- 2. Capacitances are maximum values at 25°C, measured at 1.0 MHz, with  $V_{\text{IN}}$  = 0 V.

Figure 3. Output Load Circuit

# AC ELECTRICAL CHARACTERISTICS <sup>1</sup> (See Timing Diagrams Pages 21-35)

| 0.440.01           | DESCRIPTION                                                        | -20 |     | -25 |     | -30 |     | LINUT |

|--------------------|--------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-------|

| SYMBOL             |                                                                    | MIN | MAX | MIN | MAX | MIN | MAX | UNIT  |

| fc                 | Clock Cycle Frequency                                              |     | 50  |     | 40  |     | 33  | MHz   |

| tc                 | Clock Cycle Time                                                   | 20  |     | 25  |     | 30  |     | ns    |

| tch                | Clock HIGH Time                                                    | 8   |     | 10  |     | 12  |     | ns    |

| tcL                | Clock LOW Time                                                     | 9   |     | 12  |     | 14  |     | ns    |

| t <sub>DS</sub>    | Data In Setup Time                                                 | 5   |     | 6   |     | 7   |     | ns    |

| t <sub>DSO</sub>   | Data Setup Time When Writing to Resource Register From Output Port | 10  |     | 12  |     | 14  |     | ns    |

| t <sub>DH</sub>    | Data In Hold Time                                                  | 2   |     | 2   |     | 2   |     | ns    |

| tDHO               | Data Hold Time When Writing to Resource Register From Output Port  | 2   |     | 2   |     | 2   |     | ns    |

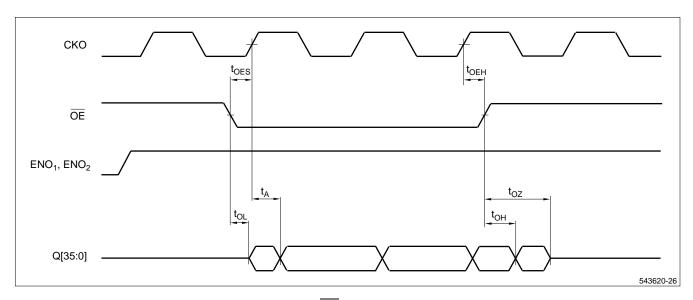

| t <sub>A</sub>     | Data Out Access Time                                               |     | 14  |     | 16  |     | 18  | ns    |

| toH                | Data Out Hold Time                                                 | 4   |     | 4   |     | 4   |     | ns    |

| t <sub>ES</sub>    | Enable Setup Time                                                  | 5   |     | 6   |     | 7   |     | ns    |

| t <sub>EH</sub>    | Enable Hold Time                                                   | 2   |     | 2   |     | 2   |     | ns    |

| toes               | Output Enable Setup Time                                           | 6   |     | 7   |     | 8   |     | ns    |

| toeh               | Output Enable Hold Time                                            | 2   |     | 2   |     | 2   |     | ns    |

| t <sub>OL</sub>    | OE to Data Out Low-Z <sup>2</sup>                                  | 1   |     | 1   |     | 1   |     | ns    |

| toz                | OE to Data Out High-Z <sup>2</sup>                                 |     | 12  |     | 15  |     | 19  | ns    |

| toe                | OE to Data Valid                                                   |     | 10  |     | 12  |     | 14  | ns    |

| ter                | Empty Flag Access Time                                             |     | 14  |     | 16  |     | 18  | ns    |

| tff                | Full Flag Access Time                                              |     | 14  |     | 16  |     | 18  | ns    |

| tAE                | AE Flag Access Time                                                |     | 14  |     | 16  |     | 18  | ns    |

| t <sub>AF</sub>    | AF Flag Access Time                                                |     | 14  |     | 16  |     | 18  | ns    |

| t <sub>HF</sub>    | HF Flag Access Time                                                |     | 14  |     | 16  |     | 18  | ns    |

| tpF                | Parity Flag Access Time                                            |     | 14  |     | 16  |     | 18  | ns    |

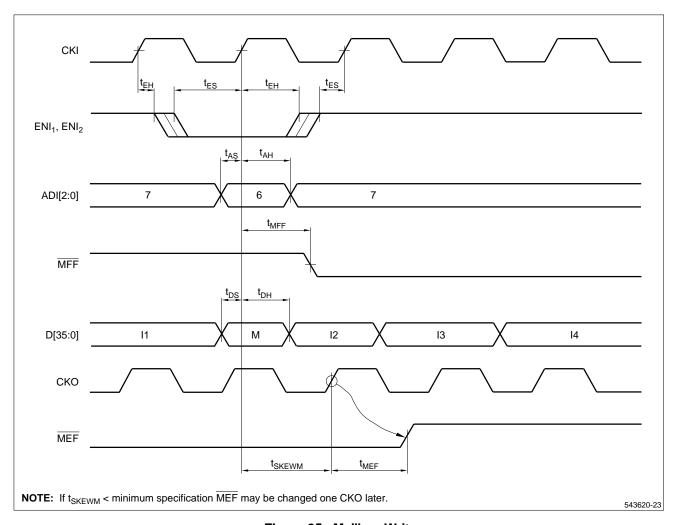

| t <sub>MFF</sub>   | Mailbox FF Access Time                                             |     | 14  |     | 16  |     | 18  | ns    |

| t <sub>MEF</sub>   | Mailbox EF Access Time                                             |     | 14  |     | 16  |     | 18  | ns    |

| t <sub>AS</sub>    | Address Setup Time                                                 | 10  |     | 12  |     | 14  |     | ns    |

| tah                | Address Hold Time                                                  | 2   |     | 2   |     | 2   |     | ns    |

| twss               | WSI and WSO Setup Time                                             | 10  |     | 12  |     | 14  |     | ns    |

| twsh               | WSI and WSO Hold Time                                              | 2   |     | 2   |     | 2   |     | ns    |

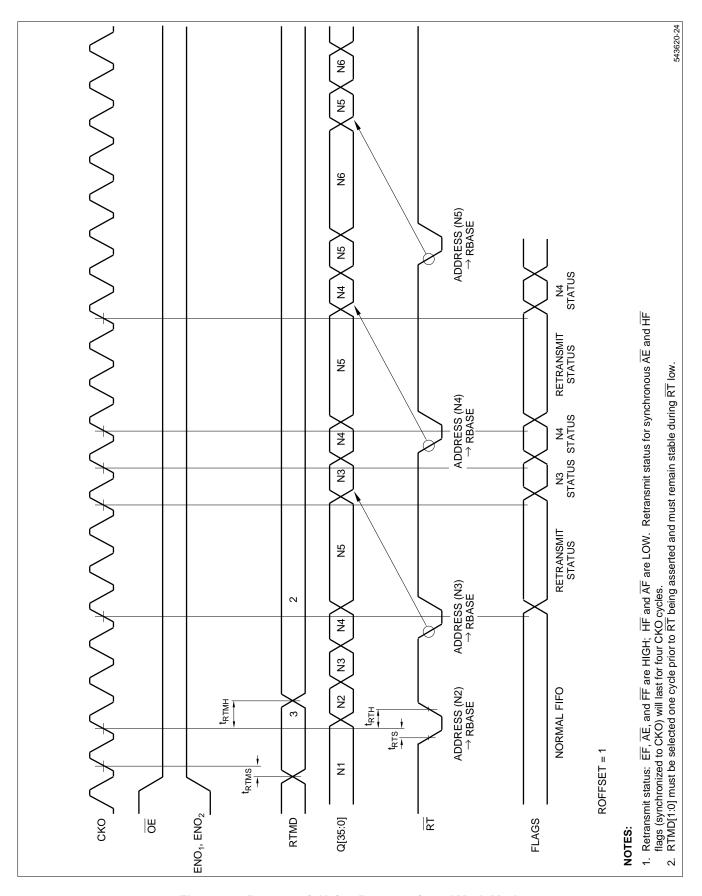

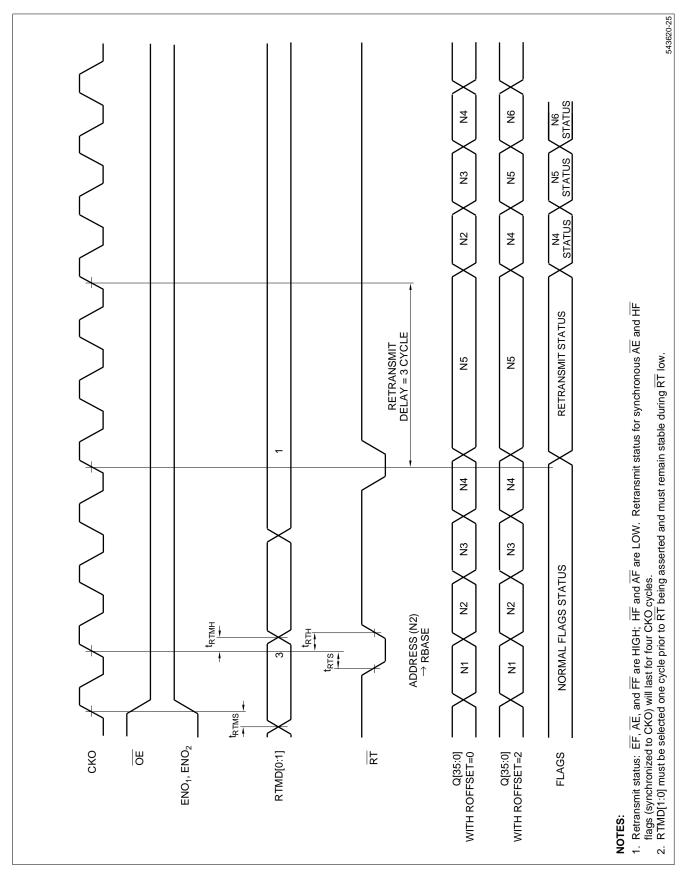

| t <sub>RTMS</sub>  | Retransmit Mode Setup Time                                         | 5   |     | 6   |     | 7   |     | ns    |

| t <sub>RTMH</sub>  | Retransmit Mode Hold Time                                          | 2   |     | 2   |     | 2   |     | ns    |

| t <sub>RTS</sub>   | Retransmit Setup Time                                              | 5   |     | 6   |     | 7   |     | ns    |

| trth               | Retransmit Hold Time                                               | 2   |     | 2   |     | 2   |     | ns    |

| t <sub>RS</sub>    | Reset Pulse Width                                                  | 20  |     | 25  |     | 30  |     | ns    |

| trsr               | Reset Recovery Time <sup>2</sup>                                   | 10  |     | 12  |     | 15  |     | ns    |

| t <sub>RF</sub>    | Reset LOW to Flag Valid                                            |     | 30  |     | 35  |     | 40  | ns    |

| t <sub>RO</sub>    | Reset to Data Out LOW                                              |     | 18  |     | 20  |     | 22  | ns    |

| t <sub>BA</sub>    | Bypass LOW to Data Valid                                           |     | 12  |     | 16  |     | 18  | ns    |

| tBD                | Bypass Propagation Delay                                           |     | 12  |     | 16  |     | 18  | ns    |

| t <sub>SKEW1</sub> | Skew Time Between CKO and CKI for FF <sup>3</sup>                  | 7   |     | 9   |     | 11  |     | ns    |

| t <sub>SKEW2</sub> | Skew Time Between CKI and CKO for EF 4                             | 7   |     | 9   |     | 11  |     | ns    |

| tskewm             | Skew Time Between Clock for Mailbox Flags                          | 7   |     | 9   |     | 11  |     | ns    |

#### NOTES:

- 1. Timing measurements performed at 'AC Test Condition' levels.

- 2. Values are guaranteed by design; not currently tested.

- 3. These times also apply to the Programmable-Almost-Full and Half-Full flags when they are synchronized to CKI.

- 4. These times also apply to the Half-Full and Programmable-Almost-Empty flags when they are synchronized to CKO.

## PIN DESCRIPTIONS (FUNCTIONAL)

| PIN NAME | ME DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | DATABUS                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| D[35:0]  | <b>36-bit Input-Port Databus.</b> The D port is the input port for the FIFO memory array, the resource registers, and the mailbox, or it may be directly connected to the output port. See Figure 4. D[35:0] is synchronous to the rising edge of CKI.                                                                                                               |  |  |  |

| Q[35:0]  | Three-State 36-Bit Output-Port Databus. The Q port is the output port for the FIFO memory array, the resource registers, and the mailbox, or it may be directly connected to the input port. See Figure 4. Q[35:0] is synchronous to the rising edge of CKO. The lower 16 bits of the Q port (Q[15:0]) may also be used as the input port for the resource register. |  |  |  |

|          | CLOCKS                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| CKI      | Input-Port Clock. CKI is a free-running waveform controlled by an oscillator. It may be irregular or asynchronous if minimum clock-HIGH times and clock-LOW times are met.                                                                                                                                                                                           |  |  |  |

| СКО      | Output-Port Clock. CKO is a free-running waveform controlled by an oscillator. It may be irregular or asynchronous if minimum clock-HIGH times and clock-LOW times are met.                                                                                                                                                                                          |  |  |  |

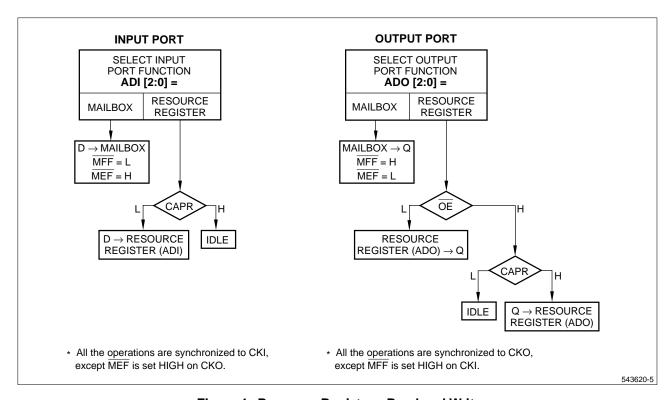

Figure 4. Resource Registers, Read and Write

| PIN NAME                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                     | ASYNCHRONOUS CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RS                                  | <b>Master Reset.</b> When asserted LOW, the LH543620 internal resource registers are set to their default value. See Table 1. The status flags indicate Empty FIFO.                                                                                                                                                                                                                                                                             |  |  |  |  |

| ŌĒ                                  | Output Enable. When asserted LOW, $\overline{OE}$ forces Q[35:0] to be active. When deasserted HIGH, $\overline{OE}$ forces Q[35:0] into a Hi-Z state. Bit 6 of the control register governs whether $\overline{OE}$ suppresses the advancement of the Read Pointer (RP). In this case, $\overline{OE}$ must obey setup time and hold time relative to CKO.                                                                                     |  |  |  |  |

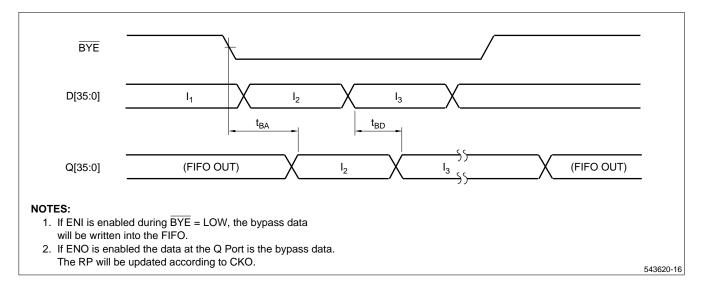

| BYE                                 | Data-Bypass Enable. When asserted LOW, BYE connects Q[35:0] directly to D[35:0].                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CAPR                                | Command-Address Port Reference. CAPR determines the source of the 16-bit word to be loaded into the resource register. Whenever CAPR is LOW, the word comes from the Input Port. Whenever CAPR is HIGH (OE is HIGH), the word comes from the Output Port.  NOTES:  1. The destination of the resource register is always the Output Port.  2. CAPR is assumed to be a steady signal. It is not allowed to change 'on-the-fly' during operation. |  |  |  |  |

|                                     | CONTROL SIGNALS SYNCHRONOUS TO THE INPUT CLOCK                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| ENI <sub>1</sub> , ENI <sub>2</sub> | Input-Port Enables. ENI <sub>1</sub> and ENI <sub>2</sub> are active HIGH and synchronous to the rising edge of CKI. Data is written into the FIFO memory array when both ENI <sub>1</sub> and ENI <sub>2</sub> are asserted HIGH.  NOTE: ENI <sub>1</sub> , ENI <sub>2</sub> DO NOT ENABLE writing data into the Resource Registers or the Mailbox.                                                                                            |  |  |  |  |

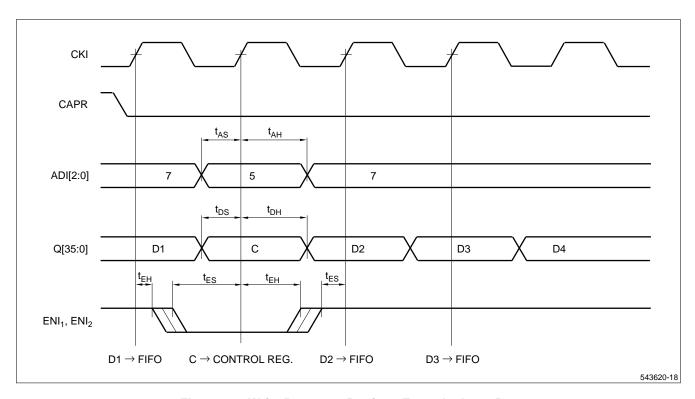

| ADI[2:0]                            | Input-Port Address. ADI[2:0] specifies the Input-Port destination. See Table 1. ADI[2:0] is synchronized to the rising edge of CKI.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

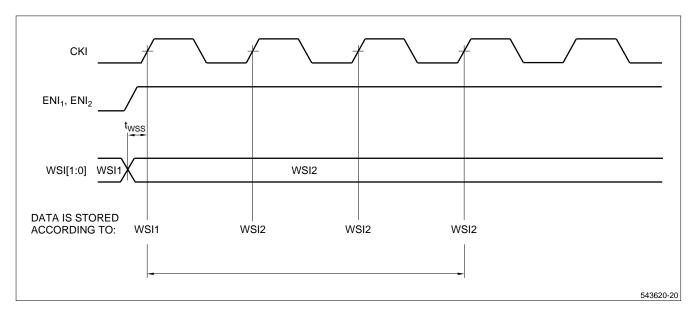

| WSI[1:0]                            | Input-Port Word-Width Selection. WSI[1:0] selects the Input-Port Word-Width. See Table 2. WSI[1:0] is synchronous to the rising edge of CKI.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

**Table 1. Input-Port Address**

| ADI <sub>2</sub> | ADI <sub>1</sub> | ADI <sub>0</sub> | SELECTION                               | DEFAULT VALUE<br>(of the selected<br>REGISTER) |

|------------------|------------------|------------------|-----------------------------------------|------------------------------------------------|

| L                | L                | L                | RBASE register                          | 0                                              |

| L                | L                | Н                | ROFFSET register                        | 0                                              |

| L                | Н                | L                | AF offset value                         | 8                                              |

| L                | Н                | Н                | Parity register                         | 0                                              |

| Н                | L                | L                | AE offset value                         | 8                                              |

| Н                | L                | Н                | Control register                        | 1                                              |

| Н                | Н                | L                | Mailbox                                 | 0                                              |

| Н                | Н                | Н                | Resource<br>registers write<br>disabled |                                                |

Table 2. Input-Port Word-Width Selection

| WSI <sub>1</sub> | WSI <sub>0</sub> | FUNCTION                                   |                   |  |

|------------------|------------------|--------------------------------------------|-------------------|--|

| L                | L                | 9-Bit Data-Path<br>Width                   | Input data D[8:0] |  |

| L                | Н                | 18-Bit Data-Path Width Input data D[17:0]  |                   |  |

| Н                | L                | Reserved                                   |                   |  |

| Н                | Н                | 36-Bit Data-Path Width  Input data D[35:0] |                   |  |

| PIN NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|            | STATUS FLAGS SYNCHRONOUS TO THE INPUT CLOCK                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| FF         | <b>Full Flag.</b> FF is synchronous to the rising edge of CKI. When asserted LOW, 1024 36-bit words of the FIFO memory array contain meaningful data. When FF is asserted, writing data to the FIFO is disabled.                                                                                                                                                                                                    |  |  |  |  |  |

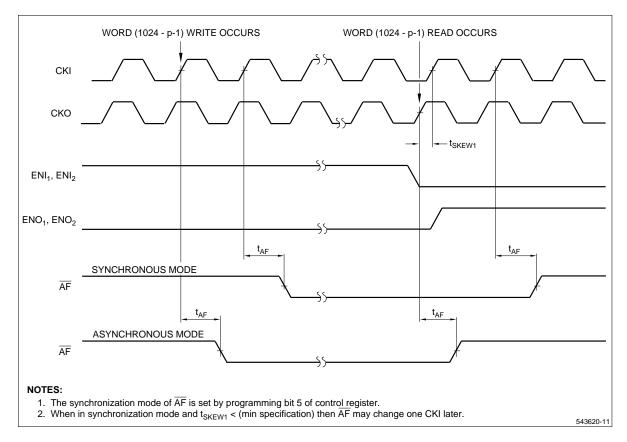

| ĀF         | Almost-Full Flag. When asserted LOW, $\overline{AF}$ indicates that there are at most 'p' vacant 36-bit words remaining in the FIFO memory array, where 'p' is the value of the Almost-Full-Offset-Value. $\overline{AF}$ has two synchronization modes depending on Bit 5 of the control register. Bit $5 = 0$ (Default) Asynchronous Mode Bit $5 = 1$ : $\overline{AF}$ is synchronous to the rising edge of CKI. |  |  |  |  |  |

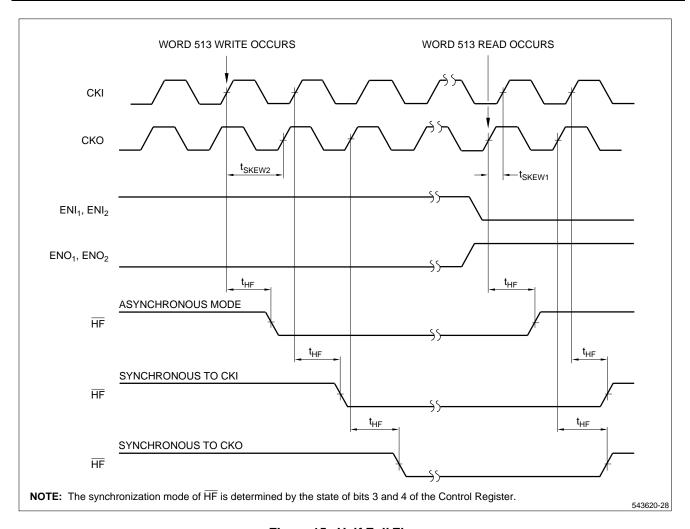

| ΉF         | Half-Full Flag. When asserted LOW, there are at least 513 36-bit words in the FIFO memory array. HF has three synchronization modes depending on Bits 3 and 4 of the control register. See Table 3.                                                                                                                                                                                                                 |  |  |  |  |  |

| MFF        | Mailbox-Full Flag. MFF is synchronized to the rising edge of CKI. When asserted LOW, it indicates that a new mail word has been placed in the mailbox.                                                                                                                                                                                                                                                              |  |  |  |  |  |

|            | CONTROL SIGNALS SYNCHRONOUS TO THE OUTPUT CLOCK                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| ENO1, ENO2 | Output-Port Enables. ENO <sub>1</sub> and ENO <sub>2</sub> are active HIGH, synchronous to the rising edge of CKO. Data is read from the FIFO memory array when both ENO <sub>1</sub> , ENO <sub>2</sub> are asserted.  NOTE: ENO <sub>1</sub> , ENO <sub>2</sub> DO NOT ENABLE reading data from the Resource Register or the Mailbox.                                                                             |  |  |  |  |  |

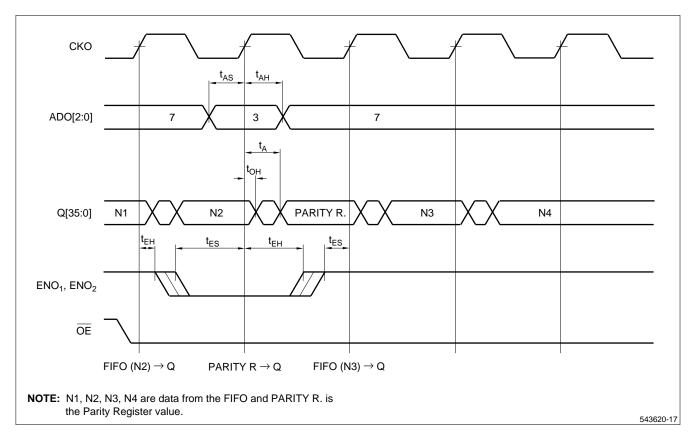

| ADO[2:0]   | Output-Port Address. ADO[2:0] specifies the Output-Port source/destination. See Table 4. ADO[2:0] is synchronous to the rising edge of CKO.  NOTE: In order to read the resource register at the output bus, BYE should be deasserted and the FIFO memory array should be disabled.                                                                                                                                 |  |  |  |  |  |

Table 3. HF Synchronization Modes

| CONTROL<br>REGISTER |    | FUNCTION                                                        |  |

|---------------------|----|-----------------------------------------------------------------|--|

| BIT 4 BIT 3         |    |                                                                 |  |

| L*                  | L* | Asynchronous Mode: HF                                           |  |

| L                   | Н  | Synchronous Mode I: HF is synchronous to the rising edge of CKC |  |

| Н                   | L  | Synchronous Mode II: HF is                                      |  |

| Н                   | Н  | synchronous to the rising edge of CKI                           |  |

<sup>\*</sup> Default Mode

Table 4. Output-Port Address

| ADO <sub>2</sub> | ADO <sub>1</sub> | ADO <sub>0</sub> | SELECTION                              | DEFAULT VALUE<br>(of the selected<br>REGISTER) |

|------------------|------------------|------------------|----------------------------------------|------------------------------------------------|

| L                | L                | L                | RBASE<br>register                      | 0                                              |

| L                | L                | Н                | ROFFSET register                       | 0                                              |

| L                | Н                | L                | AF offset value                        | 8                                              |

| L                | Н                | Н                | Parity register                        | 0                                              |

| Н                | L                | L                | AE offset value                        | 8                                              |

| Н                | L                | Н                | Control register                       | 1                                              |

| Н                | Н                | Г                | Mailbox                                | 0                                              |

| Н                | Н                | Н                | Resource<br>registers read<br>disabled | Not applicable                                 |

| PIN NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|           | CONTROL SIGNALS SYNCHRONOUS TO THE OUTPUT CLOCK (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

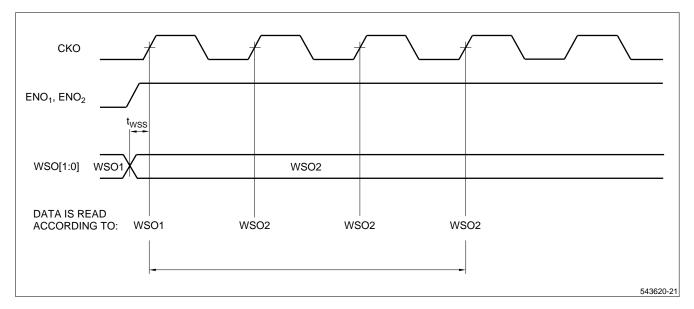

| WSO[1:0]  | Output-Port Word-Width Selection. WSO[1:0] is synchronous to the rising edge of CKO. WSO[1:0] selects the Output-Port Word-Width and controls byte-order-reversal according to Table 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RTMD[1:0] | Retransmit Mode Control. RTMD[1:0] is synchronized to the rising edge of CKO. RTMD[1:0] controls the placement of new contents into the Read Pointer (RP) and/or the Retransmit Base (RBASE) registers. Whenever Retransmit (RT) is asserted, one of three operations is performed according to the setting of RTMD[1:0]. See Table 6.  NOTES:  1. When RTMD[1:0] is set to 0, the FIFO is in depth cascade mode, and the Retransmit mechanism can not be used. In cascade mode, the Almost-Empty Flag is a handshake signal for cascading. The Almost-Empty Flag is used as an input to the ENI of the next FIFO in the chain.  2. In standard FIFO operation RTMD[1:0] must not be set to 0 and the Retransmit signal must be HIGH. |  |  |  |  |

| RT        | Retransmit. $\overline{RT}$ is synchronized to the rising edge of CKO. When asserted LOW, $\overline{RT}$ causes one of the Retransmit Mode operations to be performed, according to the encoding of RTMD[1:0]. See Table 6.  NOTE: When RTMD[1:0] = 0 (FIFO is in cascade mode) $\overline{RT}$ is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

Table 5. Output-Port Word-Width Selection

| WSO <sub>1</sub> | WSO <sub>0</sub> | FUNCTION                                               |                     |  |

|------------------|------------------|--------------------------------------------------------|---------------------|--|

| L                | L                | 9-Bit Data-Path<br>Width                               | Output data Q[8:0]  |  |

| L                | Н                | 18-Bit Data-Path Width Output data Q[17                |                     |  |

| Н                | L                | 36-Bit Data-Path<br>Width With Byte-<br>Order-Reversal | Output data Q[35:0] |  |

| Н                | Н                | 36-Bit Data-Path<br>Width                              | Output data Q[35:0] |  |

Table 6. Retransmit Operation Modes

| RTMD <sub>1</sub> | RTMD <sub>0</sub> | OPERATION                | ACTION TAKEN                                                            |

|-------------------|-------------------|--------------------------|-------------------------------------------------------------------------|

| L                 | L                 | Depth<br>Cascade<br>Mode | The Almost-Empty Flag is a handshake signal for cascading               |

| L                 | Н                 | Retransmit               | (RBASE) +<br>(ROFFSET) → RP                                             |

| Н                 | L                 | Retransmit<br>and Mark   | (RBASE) +<br>(ROFFSET) → RP<br>and<br>(RBASE) +<br>(ROFFSET) →<br>RBASE |

| Н                 | Н                 | Mark                     | (RP) → RBASE                                                            |

| PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | STATUS FLAGS SYNCHRONOUS TO THE OUTPUT CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

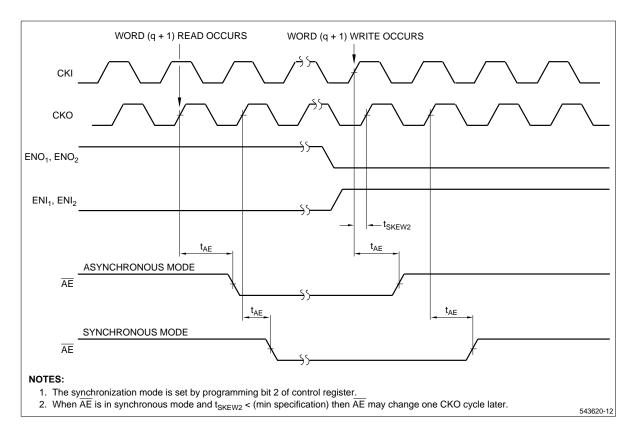

| ĀĒ       | Almost-Empty Flag. The AE flag has two modes of operation depending on the RTMD[1:0] setting.  1. RTMD[1:0] ≠ 0: AE is a standard Almost-Empty Flag. When asserted LOW, AE implies that there are at most 'q' 36-bit words in the FIFO memory array, where 'q' is Almost-Empty-Offset-Value register value. In this mode AE has two synchronization options depending on the setting of Bit 2 of the control register.  Bit 2 = 0 (Default) Asynchronous Mode  Bit 2 = 1 Synchronous Mode: AE is synchronous to the rising edge of CKO.  2. RTMD[1:0] = 0: AE is a handshake signal for cascading.                                                            |  |  |  |

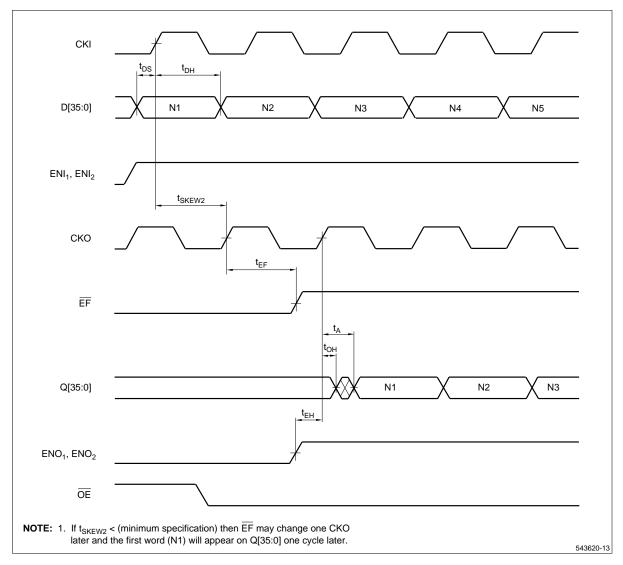

| ĒĒ       | <b>Empty Flag.</b> $\overline{\text{EF}}$ is synchronous to the rising edge of CKO. When asserted LOW, all 1024 36-bit words are vacant. When asserted, $\overline{\text{EF}}$ disables the FIFO Read operation.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

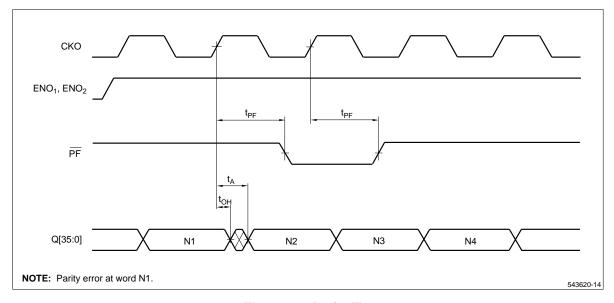

| PF       | Parity-Error Flag. $\overline{PF}$ is synchronized to the rising edge of CKO. When asserted LOW, $\overline{PF}$ implies that a parity error has occurred in at least one 9-bit byte within a 36-bit word read from the FIFO memory array. If there are no errors, it is deasserted HIGH. When an error is detected, the parity check result of each 9-bit byte of the 36-bit output word is written to the parity register. The content of the parity register is frozen until read. The $\overline{PF}$ signal is delayed by one CKO cycle compared to the output data (i.e., if the $\overline{PF}$ is asserted, there was an error in the previous word). |  |  |  |

| MEF      | Mailbox-Empty Flag. MEF is synchronous to the rising edge of CKO. When asserted LOW, MEF indicates that there is no new mail word in the mailbox.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|          | VOLTAGES AND GROUNDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Vcc      | Positive Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Vss      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

#### **OPERATIONAL DESCRIPTION**

The LH543620 has four operating modes:

Normal Mode

Programmable Resource Registers

Mailbox

**Data Bypass**

#### **NORMAL MODE**

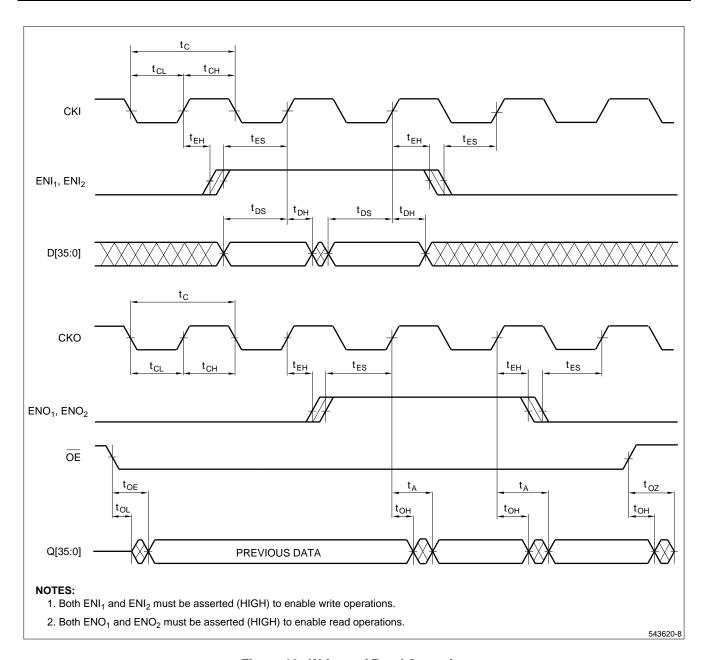

Normal FIFO operation refers to Read and Write operations to the FIFO memory array. Data Write operations into the FIFO memory array occur at the rising edge of CKI. The operation is enabled if both ENI<sub>1</sub> and ENI<sub>2</sub> are asserted HIGH. Data Read operations from the FIFO memory occur at the rising edge of CKO. The operation is enabled if both ENO<sub>1</sub> and ENO<sub>2</sub> are asserted HIGH.

The FIFO write and read operations are supported by the following mechanisms:

Byte-Order-Reversal and Bus Funneling/Defunneling Functions

Status Flags

Retransmit Mechanism

Parity Checking

**Parity Generation**

#### Byte-Order-Reversal and Bus Funneling/ Defunneling Functions

Word width can be selected at the Input Port and/or the Output Port to be 36, 18 or 9 bits wide. When the Output Port width is selected to be 36 bits, it is possible to select Byte-Order-Reversal.

The funneling mechanism is controlled by the inputs WSI[1:0] and WSO[1:0] according to Tables 2 and 5. Data is packed and unpacked from a 36-bit word memory array. Table 7 describes all combinations of funneling/defunneling.

Changes to the funneling/defunneling settings during system operation should be made one clock before a word boundary, as shown in Example 3.

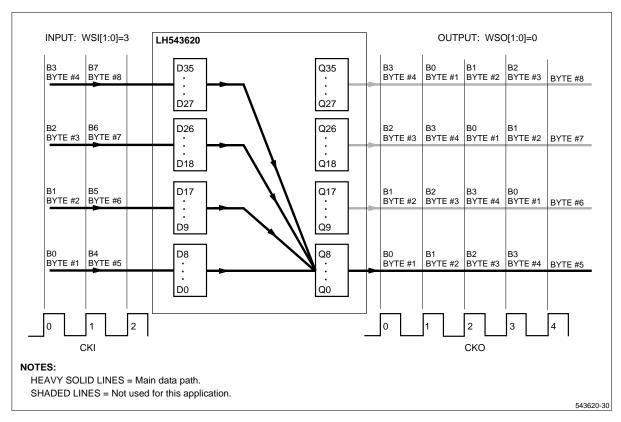

Example 1: 36-to-9 Funneling

| CONDIT            | TIONS | RESULTS                                      |

|-------------------|-------|----------------------------------------------|

| WSI[1:0] WSO[1:0] |       | RESULTS                                      |

| 3                 | _     | Input 36 bits wide.                          |

| _                 | 0     | Output 9 bits wide.<br>Pins used are Q[8:0]. |

The dataflow structure is illustrated by Figure 5.

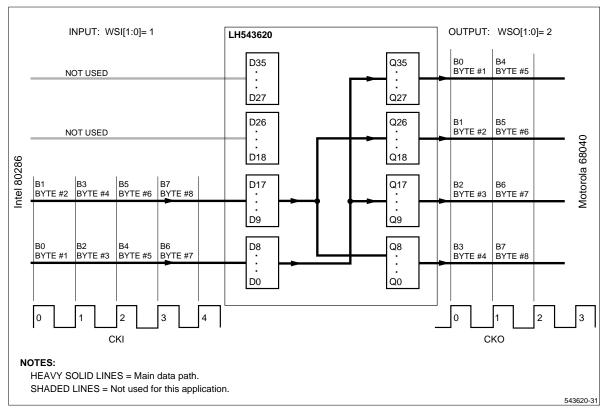

Example 2: 18-to-36 Defunneling With Byte Reversal

This example performs two functions:

- 1. Bus width change

- 2. Big Endian to Little Endian conversion

This configuration can be used for connecting the Intel 80286 to the Motorola 68040.

| CONDI             | TIONS | RESULTS                                       |

|-------------------|-------|-----------------------------------------------|

| WSI[1:0] WSO[1:0] |       | RESOLIS                                       |

| 1                 | _     | Input 18 bits wide. Pins used are D[17:0].    |

| _                 | 2     | Output 36 bits wide with byte order reversal. |

The dataflow structure is illustrated by Figure 6.

Example 3: Changing Input Bus Width From 9 to 36 During Operation

| CKI | WSI | ACTION                |  |  |  |  |  |

|-----|-----|-----------------------|--|--|--|--|--|

| 0   | 0   | Write 1st 9-bit byte  |  |  |  |  |  |

| 1   | 0   | Write 2nd 9-bit byte  |  |  |  |  |  |

| 2   | 0   | Write 3rd 9-bit byte  |  |  |  |  |  |

| 3   | 3   | Write 4th 9-bit byte  |  |  |  |  |  |

| 4   | 3   | Write 1st 36-bit word |  |  |  |  |  |

Table 7. Bus Funneling/Defunneling \*

| INPUT  |         |        |            | OUTPUT |         |    |     |      |         |         |         |    |                         |                         |    |           |         |    |        |        |    |

|--------|---------|--------|------------|--------|---------|----|-----|------|---------|---------|---------|----|-------------------------|-------------------------|----|-----------|---------|----|--------|--------|----|

| СКІ    | WSI = 0 |        |            | СКО    | WSO = 3 |    |     |      | WSO = 2 |         |         |    | WSO = 1                 |                         |    |           | WSO = 0 |    |        |        |    |

| cycles | [       | D[35:9 | ]          | D[8:0] | cycles  |    | Q[3 | 5:0] |         | Q[35:0] |         |    | Q[35:18] <b>Q[17:0]</b> |                         |    |           | Q[35:9] |    |        | Q[8:0] |    |

| 0      |         | XXX    |            | В0     | 0       | В3 | B2  | B1   | В0      | В0      | B1      | B2 | В3                      | В3                      | B2 | B1        | В0      | В3 | B2     | B1     | В0 |

| 1      |         | XXX    |            | B1     | 1       | B7 | B6  | B5   | B4      | B4      | B5      | B6 | B7                      | B1                      | B0 | B3        | B2      | В0 | В3     | B2     | B1 |

| 2      |         | XXX    |            | B2     | 2       |    |     |      |         |         |         |    |                         | B7                      | B6 | B5        | B4      | B1 | B0     | В3     | B2 |

| 3      | xxx     |        | B3         | 3      |         |    |     |      |         |         |         |    | B5                      | B4                      | B7 | <b>B6</b> | B2      | B1 | B0     | B3     |    |

| 4      |         | XXX    |            | B4     | 4       |    |     |      |         |         |         |    |                         |                         |    |           |         | B7 | B6     | B5     | B4 |

| 5      |         | XXX    |            | B5     | 5       |    |     |      |         |         |         |    |                         |                         |    |           |         |    |        |        |    |

| 6      |         | XXX    |            | B6     | 6       |    |     |      |         |         |         |    |                         |                         |    |           |         |    |        |        |    |

| 7      |         | XXX    |            | B7     | 7       |    |     |      |         |         |         |    |                         |                         |    |           |         |    |        |        |    |

| 8      |         | XXX    |            | B8     | 8       |    |     |      |         |         |         |    |                         |                         |    |           |         |    |        |        |    |

|        | WSI = 1 |        |            |        | WSO = 3 |    |     |      | WSO = 2 |         |         |    | WSO = 1                 |                         |    |           | WSO = 0 |    |        |        |    |

|        | D[35    | 5:18]  | D[         | 17:0]  |         |    | Q[3 | 5:0] |         |         | Q[35:0] |    |                         | Q[35:18] <b>Q[17:0]</b> |    |           | Q[35:9] |    |        | Q[8:0] |    |

| 0      | Х       | X      | B1         | B0     | 0       | B3 | B2  | B1   | B0      | B0      | B1      | B2 | B3                      | В3                      | B2 | B1        | B0      | В3 | B2     | B1     | В0 |

| 1      | Х       | X      | <b>B</b> 3 | B2     | 1       | B7 | B6  | B5   | B4      | B4      | B5      | B6 | B7                      | B1                      | B0 | <b>B3</b> | B2      | B0 | В3     | B2     | B1 |

| 2      | Х       | X      | B5         | B4     | 2       |    |     |      |         |         |         |    |                         | B7                      | B6 | B5        | B4      | B1 | B0     | В3     | B2 |

| 3      | Х       | X      | B7         | B6     | 3       |    |     |      |         |         |         |    |                         | B5                      | B4 | B7        | B6      | B2 | B1     | B0     | B3 |

| 4      | Х       | X      | B9         | B8     | 4       |    |     |      |         |         |         |    |                         |                         |    |           |         | B7 | B6     | B5     | B4 |

|        | WSI = 3 |        |            |        | WSO = 3 |    |     |      | WSO = 2 |         |         |    | WSO = 1                 |                         |    |           | WSO = 0 |    |        |        |    |

|        | D[35:0] |        |            |        | Q[35:0] |    |     |      | Q[35:0] |         |         |    | Q[35:18] <b>Q[17:0]</b> |                         |    | Q[35:9]   |         |    | Q[8:0] |        |    |

| 0      | B3      | B2     | B1         | В0     | 0       | B3 | B2  | B1   | B0      | B0      | B1      | B2 | B3                      | В3                      | B2 | B1        | B0      | В3 | B2     | B1     | В0 |

| 1      | B7      | B6     | B5         | B4     | 1       | B7 | B6  | B5   | B4      | B4      | B5      | B6 | B7                      | B1                      | B0 | B3        | B2      | В0 | В3     | B2     | B1 |

|        |         |        |            |        |         |    |     |      |         |         |         |    |                         | B7                      | B6 | B5        | B4      | B1 | В0     | В3     | B2 |

|        |         |        |            |        |         |    |     |      |         |         |         |    |                         | B5                      | B4 | B7        | B6      | B2 | B1     | B0     | В3 |

|        |         |        |            |        |         |    |     |      |         |         |         |    |                         |                         |    |           |         | B7 | B6     | B5     | B4 |

<sup>\*</sup> NOTE: B0, B1, . . ., represent data bytes.

Figure 5. Example of 36-to-9 Bus Funneling

Figure 6. Example of 18-to-36 Bus Defunneling

With Byte Order Reversal

#### Status Flags

There are five status flags:

FF Full Flag

AF Almost-Full Flag

HF Half-Full Flag

AE Almost-Empty Flag

**EF** Empty Flag

The functionality and the synchronization of the status flags are detailed in the *Pins Descriptions (Functional)* section. All status flags are generated for 36-bit word widths, not according to selected input or output port widths.

#### **Retransmit Mechanism**

With standard FIFO operations, every data word can be read out of the FIFO once. The Retransmit mechanism allows reading the data more than once by providing flexible control of the Read Pointer.

Associated with the Retransmit mechanism are three control lines: RTMD[1:0], RT, and two Resource registers: RBASE and ROFFSET.

RTMD[1:0] sets the mode of operation. See Table 6.

RT enables the operation synchronous to CKO.

Retransmit allows three modes of operation:

Mark: RTMD[1:0] = 3 and  $\overline{RT}$  is asserted. The value of the Read Pointer is saved into the RBASE register.

Retransmit: RTMD[1:0] = 1 and  $\overline{RT}$  is asserted. The Read Pointer is loaded by the value of RBASE plus the value of ROFFSET.

Retransmit and Mark: RTMD[1:0] = 2 and  $\overline{RT}$  is asserted: The Read Pointer is loaded by the value of RBASE plus the value of ROFFSET. Then the value of the Read Pointer is saved into the RBASE register.

The timing of the retransmit is illustrated in Figures 26 and 27.

When RT is asserted and RTMD[1:0] is set to 1 or 2, the flags change their value to indicate a 'Retransmit state', i.e., EF, AE, FF deasserted; AF, HF asserted. Three enable-read cycles are required to read the new data word. The flags reflect the new status. The retransmit is acknowledged even when the output is disabled (ENO = LOW), but enable-read cycles are needed to fill the pipeline with new information before reading the new data.

#### **NOTES**

- 1. The Retransmit mechanism can be used independently and parallel to the write operation.

- RTMD[1:0] must be selected two cycles prior to RT being asserted and remain stable during RT low.

- 3. At least two words need to be in the FIFO memory array prior to performing a retransmit.

- 4. When using normal read and write operations, the FF inhibits writing when the FIFO is full and the EF inhibits reading when the FIFO is empty. This behavior provides a protection from wraparound situations (i.e., the Read pointer is ahead of the Write Pointer). This protection is NOT provided when using retransmit. The user should be careful not to write more than 1024 words from the marked point.

- 5. When the retransmit mechanism is not used, the recommended connection is:

$$\frac{\mathsf{RTMD}[1:0] = 3}{\mathsf{RT} = \mathsf{HIGH}}$$

The Retransmit mechanism can be useful in many applications. For example:

1. Computer-communications applications.

When the receiver reads a block of data and finds no errors in the data block, it can mark the beginning of the new message by setting the FIFO in MARK mode RTMD[1:0] = 3 and assert the  $\overline{RT}$  signal for one clock cycle.

If the receiver finds an error in the data block, it can read the last message again by setting the FIFO in Retransmit mode RTMD[1:0] = 1 and asserting the  $\overline{RT}$  signal for one cycle.

2. Overlap addressing for DSP applications.

A typical DSP consists of A/D-FIFO-DSP. In many applications, the DSP needs to read a block of data where each block overlaps the previous block (like the overlap-and-save method for filtering.) The overlap addressing can be implemented by using the LH543620 with no additional hardware as follows:

The FIFO is set to retransmit and mark mode: RTMD[1:0] = 2, the  $\overline{AF}$  offset register is programmed to N = Block Size, and the ROFFSET register is programmed to (N – Overlap). The data is loaded into the FIFO each time CKin is triggered.

The DSP can sense the  $\overline{AF}$  flag of the FIFO. Whenever this flag is being asserted, a new block of data is available in the FIFO. The DSP then reads a block of data, and then asserts the FIFO's  $\overline{RT}$  signal, which causes the RP and RBASE register to be set at the beginning of the new block.

#### **Parity Checking**

The Parity checking mechanism is always active. Parity checking is done separately for each of the 9-bit bytes of the 36-bit word read from the memory array. Toggling Bit 0 of the control register selects odd or even parity. When a parity error is detected in one or more bytes, the signal PF is asserted and the result of the individual parity checks are written to the parity register. See Example 3.

To avoid a possible invalid  $\overline{PF}$  signal, ENO<sub>1</sub> and ENO<sub>2</sub> should not be deasserted during the CLKO low time.

The parity register is frozen until read. When read, the parity register is released and ready to store the next parity error data.

#### **Parity Generation**

After Reset, parity generation is not active. Parity generation is active only when Bit 1 of the control register is HIGH. The parity mechanism, when enabled, creates a parity bit for each of the bytes of the input word. The parity bit for each byte is created based on its 8 least significant bits of each 9-bit byte of the input-data word and on Bit 0 of the control register (it specifies odd or even parity). The result of the parity generation is written back to the MSB of the data byte. See Example 4.

#### PROGRAMMABLE RESOURCE REGISTERS

The LH543620 has six programmable resource registers. The resource registers may be loaded from either the Input Port or the Output Port. They can be read from the Output Port. The selection and loading or reading of the resource registers is controlled by ADI, ADO and CAPR. See Tables 1 and 4 and Figure 4.

The resource registers are:

Control (Default = 1).

$\overline{AE}$  Offset – Offset value of the  $\overline{AE}$  flag (Default = 8).

$\overline{AF}$  Offset – Offset value of the  $\overline{AF}$  flag (Default = 8).

$\overline{\mathsf{RT}}$  Offset – Offset value of the Retransmit mechanism (Default = 0).

$\overline{RT}$  Base – Base register of the Retransmit mechanism (Default = 0).

D0

Parity

#### EXAMPLE 3 PARITY CHECK

Q35

Output word: 100111100 000111100 100111000 000111000

Odd parity: Parity Register = 0110; PF-Asserted Low Even parity: Parity Register = 1001; PF-Asserted Low

D35

#### **EXAMPLE 4**

#### **PARITY GENERATION**

| Input word:          | <b>1</b> 00111100 | <b>0</b> 00111100 | <b>1</b> 00111000 | <b>0</b> 00111000 |

|----------------------|-------------------|-------------------|-------------------|-------------------|

| Output, odd parity:  | <b>1</b> 00111100 | <b>1</b> 00111100 | <b>0</b> 00111000 | <b>0</b> 00111000 |

| Output, even parity: | <b>0</b> 00111100 | <b>0</b> 00111100 | <b>1</b> 00111000 | <b>1</b> 00111000 |

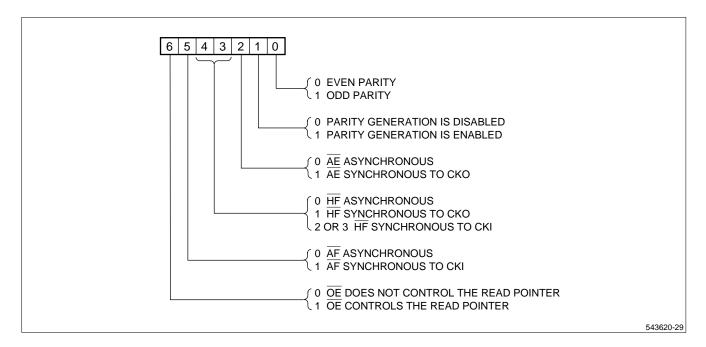

Control Register (See Figure 7)

After reset, the control register's value is 1. This sets the following conditions:

Odd parity

Disabling parity generation (parity check is active).

AF, HF, AE flags are asynchronous.

OE signal does not control the Read pointer.

#### Read/Write Resource Register Mode

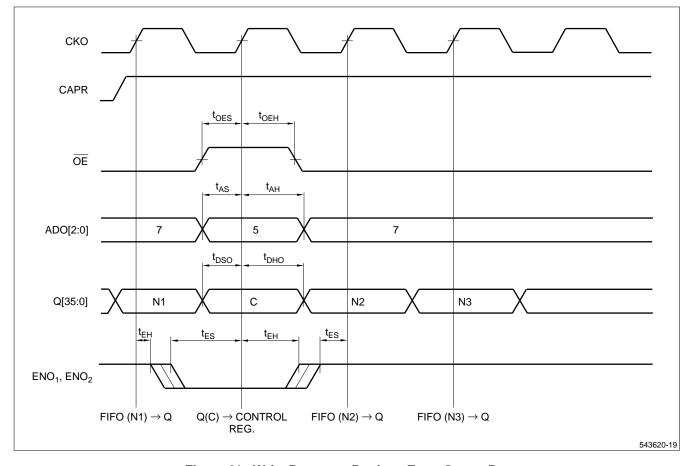

It is possible to write to the resource registers from either the Input Port or the Output Port. Reading from the resource register is possible only from the Output Port. The source port for the write operation is determined by the control signal CAPR.

Input Port:

Data from the Input Port is written to a resource register when:

the value of the input-address field, ADI, selects the register (see Table 1)

CAPR is LOW

The operation is enabled by ADI[2:0] and synchronized to CKI.

**Output Port:**

Data from the Output Port is written to a resource register when:

the value of the output-address field, ADO, selects the register (see Table 4)

CAPR is HIGH

OE is HIGH

**NOTE:** ADI[2:0] should remain stable whenever data is coming in from the output port.

Data is read from a resource register to the Output Port when:

the value of the output-address field, ADO, selects the register (see Table 4)

OE is LOW

Both operations are enabled by ADO[2:0] and are synchronous to CKO.

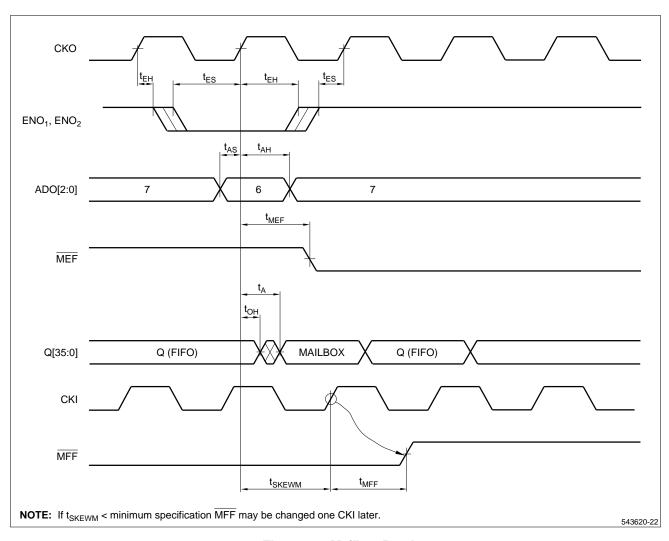

#### **MAILBOX**

The mailbox mechanism includes:

One 36-bit data register.

Two status flags:

- MFF Mailbox Full Flag

- MEF Mailbox Empty Flag

Figure 7. LH543620 Control Register

Writing to the Mailbox is enabled from the Input Port when the Input Port address field ADI[2:0] = 6. The write operation is synchronous to the rising edge of CKI.

When writing to the Mailbox, the status flags are changed as follows:

MEF is deasserted HIGH on the rising edge of CKO.

MFF is asserted LOW on the rising edge of CKI.

A Mailbox read is enabled from the Output Port, when the Output Port address field ADO[2:0] = 6. The Read operation is synchronized to CKO.

When reading the Mailbox, the status flags are changed as follows:

MEF is asserted LOW on the rising edge of CKO.

MFF is deasserted HIGH on the rising edge of CKI.

After reset the Mailbox is empty (i.e.,  $\overline{\text{MFF}} = \text{HIGH}$ ,  $\overline{\text{MEF}} = \text{LOW}$ ).

When using Mailbox, the transmitter side can transfer a message to the receiver side without interrupting the data in the FIFO memory array.

#### **DATA BYPASS MODE**

Data Bypass mode is selected when  $\overline{BYE}=LOW$ . In this mode, data may be transferred asynchronously from the Input Port to the Output Port. The device may be placed in Data Bypass mode without voiding the contents of the FIFO memory array, the Mailbox Register, or the Resource Register. However, if the input is enabled (ENI<sub>1,2</sub> = HIGH) then the input data D is also written to the FIFO memory array on the rising edge of CKI. If the Output is enabled, (ENO<sub>1,2</sub> = HIGH) then the input data D is transferred to the output buffer, and the Read Pointer is incremented by CKO. The control signal  $\overline{OE}$  is functioning when  $\overline{BYE}$  is asserted.

The recommended control setting for bypass is:

ENI = LOW, ENO = LOW, ADI[2:0] = 7, ADO[2:0] = 7,  $\overline{OE}$  = LOW,  $\overline{BYE}$  = LOW

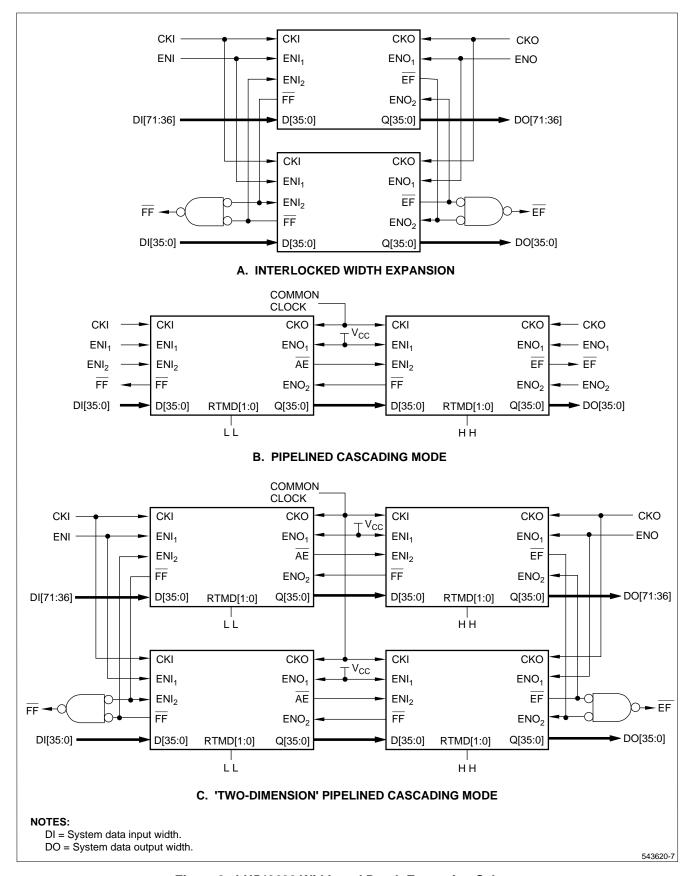

# OPERATIONAL MODES AND CONFIGURATIONS Interlocked Width Expansion (Figure 8A)

Two LH543620s may be configured to expand the width to 72 bits. This is accomplished by:

Cross-connecting the  $\overline{FF}$  output of each FIFO to ENI<sub>1</sub> (or ENI<sub>2</sub>) input of the other FIFO.

Cross-connecting the  $\overline{\text{EF}}$  output of each FIFO to ENO1 (or ENO2) input of the other FIFO.

The composite status flags are the OR function of the individual flags.

# Pipeline Cascading Mode and 'Two-Dimension' Pipeline Cascading Mode (Figure 8B and 8C)

Depth cascading is accomplished by:

Setting the upper FIFO into cascade mode: RTMD[1:0] = 0

Connecting the same free-running clock to CKO of the upper FIFO and to CKI input of the lower FIFO.

Connecting the  $\overline{AE}$  output of the upper FIFO to ENI<sub>1</sub> input (or ENI<sub>2</sub>) of the lower FIFO.

Connecting the  $\overline{FF}$  output of the lower FIFO to ENO<sub>1</sub> input (or ENO<sub>2</sub>) of the upper FIFO.

**NOTE:** RTMD[1:0] should remain stable during cascade mode operation (i.e., remain low).

Figure 8. LH543620 Width and Depth Expansion Scheme

#### **TIMING DIAGRAMS**

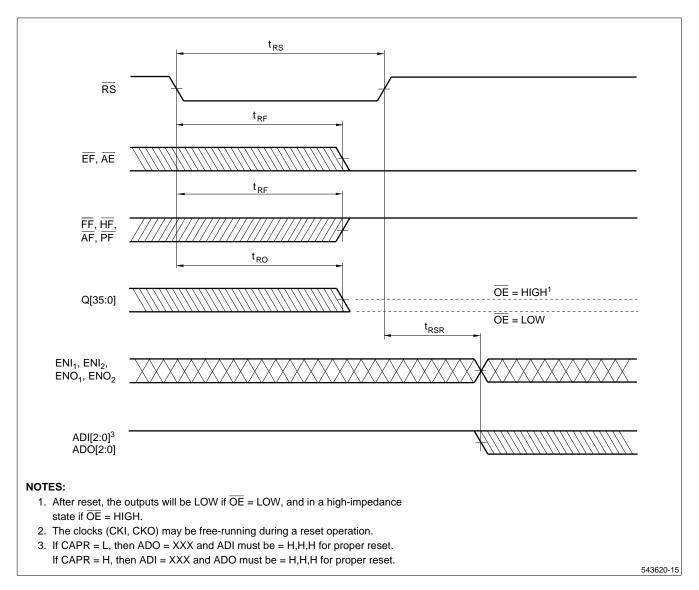

Figure 9. Reset Timing

Figure 10. Write and Read Operation

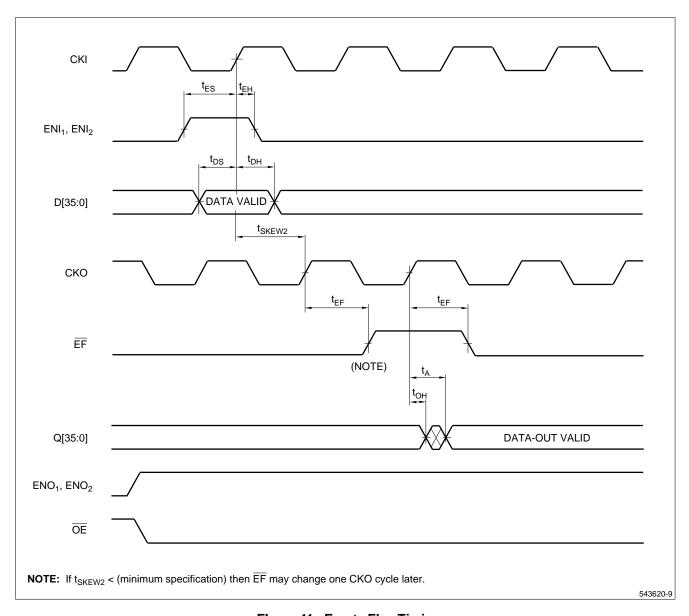

Figure 11. Empty Flag Timing

Figure 12. Full Flag Timing

Figure 13. Almost-Full Flag - Synchronous and Asynchronous Modes

Figure 14. Almost-Empty Flag - Synchronous and Asynchronous Modes

Figure 15. Half-Full Flag - Synchronous and Asynchronous Modes

Figure 16. First Word Latency

Figure 17. Parity Flag

Figure 18. Bypass

Figure 19. Read Resource Register

Figure 20. Write Resource Register From the Input Port

Figure 21. Write Resource Register From Output Port

Figure 22. WSI[1:0] Timing

Figure 23. WSO[1:0] Timing

Figure 24. Mailbox Read

**SHARP**

Figure 25. Mailbox Write

Figure 26. Retransmit Using Retransmit and Mark Mode

Figure 27. Retransmit Using Mark Mode and Retransmit Mode